# Design of a Read-Only Memory (ROM) creating square of an input using Threshold Logic Technology

Anup Kumar Biswas

Department of Computer Science and Engineering Kalyani Govt. Engineering College, Kalyani, Nadia-741235, West Bengal, India

### ABSTRACT

In this paper we will concentrate our attention on creating a Read-Only Memory (ROM) on the basis of single electron tunneling junction based threshold logic gates (TLG). Some simple and complex TLG based circuits have been discussed analytically and implemented them as well. By dint of these implemented circuits, a ROM  $(8\times4)$  is built up. With the help of thisROM and two other auxiliary terminals, a square generator of the 3-input binary numbers is presented. For verification purpose of square generator circuit, simulation test with the help of SIMON is done. For creating the logic circuits, we have a glance at a generic linear threshold gate by which a logic gate having many inputs and one output can be constructed. Threshold networks and truth tables are given in parallel in due places. State space diagram, linearly separable tests whether a function is linearly separable or not are discussed. At last, how many elements required for a TLG circuit, their processing delays and power consumption are listed. In addition, the curves regarding Delay vs. Error Probability and Delay vs. capacitance are provided. The comparison between the delays of MOS based circuits with other SET-based gate circuits is given in tabular form.

Keywords: ROM, Threshold-logic, square, tunneling, Multiple-input logic gate

Date of Submission: 18-07-2021

Date of acceptance: 04-08-2021

#### I. INTRODUCTION

AROMisamemorystoragedevicewhichpermanentbinaryinformation an be stored in or retrieved from. The researcher should specify binary information which is then fixed firmly in the unit to create the required interconnection pattern. ROMs are associated with special internal electronic fuses which are programmed for an arrangement for an identified configuration. When this patternises tablished, information stay(s) there in event hough power is turned of fand on again.

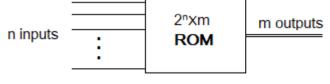

$(2^n \times m)$ ROMisgiveninFig. 1.Itcomprisesninputterminals Ablockdiagramofa and moutputterminals. Each bit combination of n bits input issaid to bean address and each bit combination that result fromtheoutput linesiscalled word. Thenumberofbitsperwordis the same а asthenumberofoutputlinesm. Anaddressisabinarynumberthatindicatesoneoftheminterms or standard products of *n* variables. The number of different addresses in the input side with *n* input variables is  $2^n$ . We can select an when a particular unique address is applied, and since there are  $2^{n}$  different addresses output word be2<sup>n</sup>member inaROM.theremust of different wordsstoredintheunit.Thewordwhich isavailableattheoutputterminals/linesatanyparticulartimereliesonthe address valueappliedtotheinputterminals.AROMis individualized by the number of words (2<sup>n</sup>) and by thenumberofbitsperword(m).

Fig.1 block diagram of a ROM

We take a 64×8 ROM. It consists of 64 words of 8 bits each. This implies that there are 8 output lines and 64 different words stored in the ROM, each of themcan be set to the output terminals. For a particular word, we want to select, will be present on the output terminals only if we determine its addressby the six input lines. There are 6input variables in a 64×8 ROM  $as^{26}=64$ , we can specify 64 addresses using 6 bits. For each address

input, there is a unique and fixed word. Thus, if the input address is 00100, the word number 4 is specified and it becomes visible on the output lines. If the input address is 11000, word number 24 is selected and sent to the output lines. There mains 64-2=62 other addresses and hey can select the other 62 words.

We specify aROMusingthetotalnumberofbitsitincludes, which is  $2^n \times m$ . For example, a 1024bit ROM may be organized as 256 words of 4 bits each. The meaning of it is that the unit bears four output terminals and 8 in putterminals to specify  $2^8 = 512$  words.

So, the maximum number of bits stored in the unit is  $512 \times 4 = 2048$ .

With reference to the inner structure, the ROM is a combinational circuit with AND gates connected as a decoder and mumber of OR gates in the unit.

TheROMisatwo-levelimplementationinsumofstandard

mofstandard products

(minterms)form.ItdoesnothavetobecomeanAND-ORimplementation,butitcanbeanyotherpossibletwolevelstandard productsimplementation.ROMshavemany differentially importantapplicationsinthedesignofa digitalcomputersystem.Theuseforimplementingmorecomplexcombinationalcircuitsisoneofthe applications[14].

#### II. DESIGN OF A READ-ONLY MEMORY

We are interested in designing a combinational circuit using a ROM. This combinational circuit performs an operation that creates a square number with respect to an input number. The circuit will take a 3-bit input variables and delivers a binary number to output terminal sequal to the square of the input number.

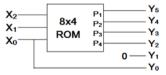

In the firststep, we aretoderivethetruthtableforthecombinational circuit. We can try to make a suitabletruthtablefortheROMbyusing particularproperties for the combinational circuit. The depicted in Table-1. There are 3 inputs and 6 outputs needed to truthtableforthecombinationalcircuitis beaccommodated all possible numbers. Noted that the output  $Y_0$  is always equal to input  $A_0$ ; so it is not required to create  $Y_0$  with a ROM as it is the same as an input variable. Moreover, output  $Y_1$  is always 0, so this output is well-known. So, it is clear that actually our need is to generate only four outputs with the ROM; the extra two bits are easily obtained. The minimum-size of ROM we shall select must have 3 inputs and 4 outputs. 3 inputs signify eight words, therefore the ROM size must be  $2^3 \times 4 = 8 \times 4$ . The ROM implementation is shown in Fig. 2. The three inputs indicates that there beingeight words and every word is having 4 bits. The other two outputs for the combinational circuit are equal to 0 and Y<sub>0</sub>. The truth table in this regard shown in Table-2. The table specifies all the information needed for programming the ROM, and the block diagram in Fig.2 shows therequiredconnections[14].

|       |        |                |       |       |       |                |       |                  |         | Table | e-2   |       |                       |                       |       |                       |

|-------|--------|----------------|-------|-------|-------|----------------|-------|------------------|---------|-------|-------|-------|-----------------------|-----------------------|-------|-----------------------|

| Tab   | ole-1  |                |       |       |       |                |       |                  |         | Inpu  | tofT  | ROM   | 01                    | tput                  | ofD   | OM                    |

| 1     | nput ( | of             |       |       |       |                |       |                  |         | -     |       |       |                       | -                     |       |                       |

|       | Circu  | it             | 0     | Dutp  | ut of | the C          | ircui | it               | Decimal | $X_2$ | $X_1$ | $X_0$ | <b>P</b> <sub>1</sub> | <b>P</b> <sub>2</sub> | $P_3$ | <b>P</b> <sub>4</sub> |

| $X_2$ | $X_1$  | $\mathbf{X}_0$ | $Y_5$ | $Y_4$ | $Y_3$ | $\mathbf{Y}_2$ |       | $\mathbf{Y}_{0}$ | output  | 0     | 0     | 0     | 0                     | 0                     | 0     | 0                     |

| 0     | 0      | 0              | 0     | 0     | 0     | 0              | 0     | 0                | 0       | 0     | 0     | 1     | 0                     | 0                     | 0     | 0                     |

| 0     | 0      | 1              | 0     | 0     | 0     | 0              | 0     | 1                | 1       | 0     | 1     | 0     | 0                     | 0                     | 0     | 1                     |

| 0     | 1      | 0              | 0     | 0     | 0     | 1              | 0     | 0                | 4       | 0     | 1     | 1     | 0                     | 0                     | 1     | 0                     |

| 0     | 1      | 1              | 0     | 0     | 1     | 0              | 0     | 1                | 9       | 1     | 0     | 0     | 0                     | 1                     | 0     | 0                     |

| 1     | 0      | 0              | 0     | 1     | 0     | 0              | 0     | 0                | 16      | 1     | °.    | 0     | •                     |                       |       | -                     |

| 1     | 0      | 1              | 0     | 1     | 1     | 0              | 0     | 1                | 25      | 1     | 0     | 1     | 0                     | 1                     | 1     | 0                     |

| 1     | 1      | 0              | 1     | 0     | 0     | 1              | 0     | 0                | 36      | 1     | 1     | 0     | 1                     | 0                     | 0     | 1                     |

| 1     | 1      | 1              | 1     | 1     | 0     | 0              | 0     | 1                | 49      | 1     | 1     | 1     | 1                     | 1                     | 0     | 0                     |

Fig. 2 A combinational circuit using a ROM.

Now with the help of Table-1 we can write the input-output relationships by means of the input variables  $X_{2}$ ,  $X_{1}$ ,  $X_{0}$  and output variables  $Y_{5}$ ,  $Y_{4}$ ,  $Y_{3}$ ,  $Y_{2}$ ,  $Y_{1}$ , and  $Y_{0}$ . Six logical expressions are written as below.

www.ijres.org

| $Y_{3} = \overline{X}_{2}X_{1}X_{0} + X_{2}\overline{X}_{1}X_{0}$<br>= $(\overline{X}_{2}X_{1} + X_{2}\overline{X}_{1})X_{0}$<br>= $(X_{1} \bigoplus X_{2})X_{0}$ (3) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Y_2 = \overline{X}_2 X_1 \overline{X}_0 + X_2 X_1 \overline{X}_0$<br>= $(\overline{X}_2 + X_2) X_1 \overline{X}_0$                                                   |

| $= X_1 \overline{X}_0(4)$<br>$Y_1 = 0(5)$                                                                                                                             |

| $\mathbf{Y}_0 = \mathbf{X}_0 \tag{6}$                                                                                                                                 |

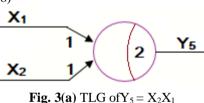

Equation (1) is an expression of an AND gate, and it is an unate function. The function is linearly separable so it can be traced as a single LTG with two inputs and one output. The threshold logic expression of equation (1) is given in equation (7) [1, 2, 3, 8, 9].

$Y_5 = sgn(X_1 + X_2 - (2)) \dots (7)$

#### 2.1 2-input AND gate

For making the threshold logic gate of an AND gate, we first draw the truth table Table-3 of AND gate and compare the weighted sum of weights  $w_1$  and  $w_2$  of two variables  $X_1$  and  $X_2$  respectively with the threshold value  $\theta$  [1,2,3,7,9].

| Table-3 |       |             |                        |          |  |

|---------|-------|-------------|------------------------|----------|--|

| $X_1$   | $X_2$ | $F(X_1X_2)$ | θ                      | Eqn. No. |  |

| 0       | 0     | 0           | $0 < \theta$           | (1)      |  |

| 0       | 1     | 0           | $w_2 < \theta$         | (2)      |  |

| 1       | 0     | 0           | $w_1 < \theta$         | (3)      |  |

| 1       | 1     | 1           | $w_1 + w_2 \ge \theta$ | (4)      |  |

|         |       |             |                        |          |  |

For positive logic, we assume weights of  $X_1$  and  $X_2$  are positive 1 each. Then from the above four inequalities in Table-3, if we assume  $w_1=1$ ,  $w_2=1$  and  $\theta=2$ , then the four inequalities or equations in 5<sup>th</sup> column in this Table-3 are satisfied. Hence the Threshold logic equation for 2-input AND gate is given in equation (8) and its corresponding threshold logic gate is drawn in Fig. 3(a)

$$Y_5 = sgn\{X_1 + X_2 - 2\}^{\dots}$$

(8)

### 2.2 For the equation (2)

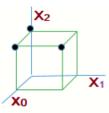

$Y_4 = X_2 \overline{X}_1 + X_2 X_0$  is anate function. Now the equation will be checked whether it is linearly separable or not. From the space plot solution point in Fig.4, the black bubbles can be separated from the colorless bubbles by a plane. The black bubbles indicate that the value of  $Y_4$  are all 1 and colorless bubbles show the value of  $Y_4$  equal to 0. As a plane can separate the black and colorless bubbles into two regions for the figure in Fig.4 so the function (2) is linearly separable and owing to this, the equation is suitable for drawing a single LTG to represent  $Y_4$ .

#### **Definition: Unatefunction**

An unate function is a Boolean function represented by a formula such that each variable appearse ither in the positive or inthe negative form throughout the formula. The functions  $f = x_1 x_2 + x_1 x_3 + x_2 x_3$  is an example of a unate function.

Now. Our intention is to obtain the threshold logic function for the expression  $Y_4 = X_2 \overline{X}_1 + X_2 X_0$ . We assume that

$Y_4(X_0, \overline{X}_1, X_2) = sgn(w_0 \cdot X_0 + w_1 \cdot \overline{X}_1 + w_2 \cdot X_2 - \theta) \dots (8)$

Fig. 4 Space plot of Y<sub>4</sub>

-----

A truth Table in support of the equations (2) and (8) is given in Table-3.

|                      | Table-3           |                            |                                      |        |  |  |  |

|----------------------|-------------------|----------------------------|--------------------------------------|--------|--|--|--|

| Inputs               | of Y <sub>4</sub> |                            | Relation of weighted                 | Eqn.   |  |  |  |

| $X_2 \overline{X}_1$ | $X_0$             | $Y_4(X_0, \bar{X}_1, X_2)$ | sum with $\theta$                    | No.    |  |  |  |

| 0 0                  | 0                 | 0                          | 0<θ                                  | (i)    |  |  |  |

| 0 0                  | 1                 | 0                          | $w_0 < \theta$                       | (ii)   |  |  |  |

| 0 1                  | 0                 | 0                          | $w_1 < \theta$                       | (iii)  |  |  |  |

| 0 1                  | 1                 | 0                          | $w_1 + w_0 < \theta$                 | (iv)   |  |  |  |

| 1 0                  | 0                 | 1                          | $w_2 \ge \theta$                     | (v)    |  |  |  |

| 1 0                  | 1                 | 1                          | $w_2 + w_0 \ge \theta$               | (vi)   |  |  |  |

| 1 1                  | 0                 | 0                          | $\tilde{w}_2 + \tilde{w}_1 < \theta$ | (vii)  |  |  |  |

| 1 1                  | 1                 | 1                          | $w_2 + w_1 + w_0 \ge \theta$         | (viii) |  |  |  |

From equation (i) in Table-3, we can say that  $\theta$  is a positive number, assume  $\theta = 2$ . If we put the  $w_0=1$ ,  $w_1=-2$  and  $w_2=3$  then all the inequalities from (i) to (viii) in Table-3 are satisfied. Hence, one solution set we have is  $\{w_0, w_1, w_2: \theta\} = \{1, -2, 3: 2\}$ . In equation (8), for the case  $\overline{X}_1$ , we are to apply the relation  $\overline{X}_1 + X_1 = 1$ , So  $\overline{X}_1 = -X_1 + 1$ .

Putting these values in equation (8), we get,

$Y_{4}(X_{0}, X_{1}, X_{2}) = sgn(w_{0} \cdot \hat{X}_{0} + w_{1} \cdot (-X_{1} + 1) + w_{2} \cdot X_{2} - \theta) \dots (8)$ = sgn(w\_{0} \cdot X\_{0} - w\_{1} \cdot X\_{1} + w\_{1} + w\_{2} \cdot X\_{2} - \theta)

Again putting the solution set  $\{w_0, w_1, w_2: \theta\} = \{1, -2, 3: 2\}$ , we get

$Y_4(X_0, X_1, X_2) = sgn(X_0 + 2X_1 + 3X_2 - 4)....(9)$

For verification the equation (9), one can put the values of  $(X_0, X_1, X_2)$  from Table-3A to the equation (9).

|       | Table-3A |       |                  |  |  |  |  |

|-------|----------|-------|------------------|--|--|--|--|

| Inp   | uts of   | FY4   |                  |  |  |  |  |

| $X_2$ | $X_1$    | $X_0$ | $Y_4(X_0X_1X_2)$ |  |  |  |  |

| 0     | 1        | 0     | 0                |  |  |  |  |

| 0     | 1        | 1     | 0                |  |  |  |  |

| 0     | 0        | 0     | 0                |  |  |  |  |

| 0     | 0        | 1     | 0                |  |  |  |  |

| 1     | 1        | 0     | 1                |  |  |  |  |

| 1     | 1        | 1     | 1                |  |  |  |  |

| 1     | 0        | 0     | 0                |  |  |  |  |

| 1     | 0        | 1     | 1                |  |  |  |  |

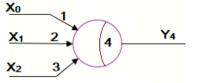

Therefore we have obtained the threshold logic equation for equation (2) and we are able to write the Threshold Logic gate for equation (9) and the corresponding diagram is given in Fig. 5.

Fig. 5 TLG of  $sgn(X_0+2X_1+3X_2-4)$

For the purpose of implementing the tunneling junction based circuit regarding the equation (9) we must find out the relevant capacitances which are essential. The values which are measured is given in Table-5.

#### 2.3 For the Third Equation

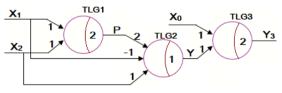

$Y_3 = (X_1 \bigoplus X_2) X_0 \dots (3)$

In this equation, there is an expression of Exclusive-OR, which is not linearly separable, as a whole the equation (3) is not linearly separable. So the  $Y_3$  cannot be expressed with a LTG. We will not be able to construct the circuit by using two LTGs.

When we want to express  $Y = (X_1 \bigoplus X_2) = (X_1 \cdot \overline{X}_2 + \overline{X}_1 \cdot X_2)$  with a threshold logic gate, first we express  $P = (X_1 \cdot \overline{X}_2)$  with the help of threshold gate-based equation as given in equation (8). We can write as- $P = sgn \{X_1 + \overline{X}_2 - 2\}^{\dots}$  (10)

We know  $\overline{X}_2 + X_2 = 1$  or  $\overline{X}_2 = -X_2 + 1$ , so equation (10) will be

$P = sgn \{ X_1 - X_2 - (1) \}^{\dots} (11)$

Now the Boolean expression  $Y = (X_1 \bigoplus X_2) = (X_1 \cdot \overline{X}_2 + \overline{X}_1 \cdot X_2)$  can be written as

$$Y = P + \overline{X}_1 \cdot X_2^{\dots} \tag{12}$$

For finding out the threshold gate logic of equation (12), we draw the truth Table-4. There are four inequalities in  $5^{th}$  column in this table. Note that in equation 3 there are two variables  $X_1$  and  $X_2$ , though it seems that P is a variable in equation (12), it would not be correct. Only two variables  $X_1$  and  $X_2$  are the fact and P is depending on  $X_1$  and  $X_2$ .

|       | Table-4        |   |   |                        |  |  |  |  |

|-------|----------------|---|---|------------------------|--|--|--|--|

| $X_1$ | X <sub>2</sub> | Р | Y | θ                      |  |  |  |  |

| 0     | 0              | 0 | 0 | 0< <del>0</del>        |  |  |  |  |

| 0     | 1              | 0 | 1 | $W_2 \ge \theta$       |  |  |  |  |

| 1     | 0              | 1 | 1 | $W_1 + W_3 \ge \theta$ |  |  |  |  |

| 1     | 1              | 0 | 0 | $W_1 + W_2 < \theta$   |  |  |  |  |

After solving the inequalities in the 5<sup>th</sup> column of Table-4, we obtain a solution set {  $W_1$ ,  $W_2$ ,  $W_3$ ;  $\theta$  } = {-1, 1, 2 : 1}. Hence the Threshold equation for the Y is

$Y = sgn\{-X_1 + X_2 + 2P - (1)\}^{(13)}$

Last we consider the equation (3) as  $Y_3 = (X_1 \bigoplus X_2) X_0 = Y X_0$  which is equivalent to an AND gate expression. Like a Threshold logic expression of an AND gate, we can write

Fig.6 TLG of  $Y_3 = (X_1 \bigoplus X_2) X_0$

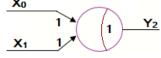

#### **2.4** For the equation (4)

$Y_2 = X1\overline{X}_{0}$ , we observe that it is a Boolean expression of an AND gate. So according to equation (11), the threshold logic equation of  $Y_2 = X_1\overline{X}_0$  will be as equation (15).

$$P = sgn \{ -X_0 + X_1 - (1) \}$$

And the threshold logic gate of equation (15) will be as in Fig. 7,

Fig.7 TLG of  $Y_2 = X_1 \overline{X}_0$

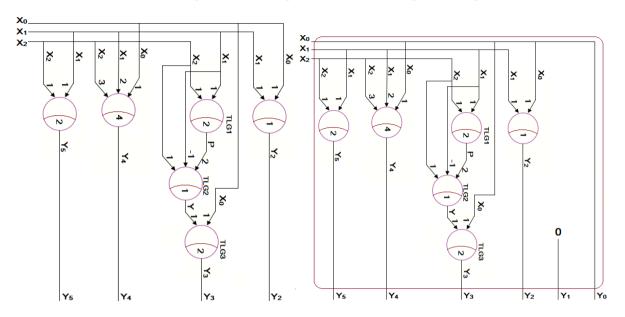

Based on the six equations starting from (1) to (6) we have been able to build their corresponding TLG gates for the equations from (1) to (4) and the remaining two equations (5) and (6) do not require such implementations. We have drawn the ROM based square circuit using TLGs and which is depicted in Fig.8.

Fig. 8(a) ROM circuit of 3-inpt and 4-output ||Fig. 8(b) Square calculation circuit of 3-bit input using TLG

#### III. GENERAL PURPOSE MULTIPLE INPUT THRESHOLD LOGIC GATE

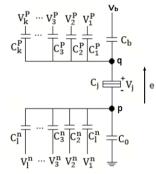

The figure drawn in Fig.9 is called multiple threshold logic gate [1, 2, 3, 4, 9, 10, 11] consisting of a tunnel junction having capacitance  $C_j$  and resistance  $R_j$ , two multi-input-signals  $V_k^P$ s and  $V_l^n$ s joined at two points 'q' and 'p' respectively. Each input voltage  $V_k^P$  is connected to the point "q" through their respectivecapacitances  $C_k^P s$ ; and each other input voltage  $V_l^n$ , is joined at the point "p" through their respective capacitances  $C_l^n$ s. The supply voltage voltage  $V_b$  is connected to the point "q" through a true capacitor  $C_b$ . Junction capacitor  $C_j$  is connected to point "p" which is connected in series with capacitor  $C_0$  which is grounded. LTGs can be constructed by means of a function presented by the signun function of h(x) expressed by equations (16a) and 16b).

Fig.9Threshold logic gate with multi-input

$g(x) = \operatorname{sgn}\{h(x)\} = \begin{cases} 0, & \text{if } h(x) < 0 \\ 1, & \text{if } h(x) \ge 0 \end{cases}$   $h(x) = \sum_{k=1}^{n} (w_k \times x_k) - \theta \qquad (16b)$ where  $x_k$  = n-Boolean inputs and  $w_k$  being their corresponding *n* integer weights.

The LTG compares the weighted sum of the inputs  $\sum_{k=1}^{n} (w_k \times x_k)$  and the threshold value $\theta$ . When the weighted sum-value  $\sum_{k=1}^{n} (w_k \times x_k)$  is greater than or equal to the threshold value  $\theta$  then output of the LTG will be high (logical "1"), otherwise it will become low (logical "0").

## IMPLEMENTATION OF ROM

IV.

Now we are interested in making the ROM  $(8\times4)$ by using the threshold logic based on the Fig. 9. For different logic gates the values of the parameters required for them will be different. After analyzing different threshold logic expressions, the corresponding parameters are measured and found out. The list of parameters for the TLGs relevant to their threshold logic expression for the purpose of implementing the Read-only memory (ROM) are given in Table-5.

| Table-5 |                                                                                     |                       |                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sl.No.  | expressions                                                                         | Name of<br>Expression | Parameters                                                                                                                                                                                                                                                                             |  |  |  |  |

| 1       | $Y_{5} = X_{2}X_{1}$<br>$Y_{5} = sgn\{X_{1} + X_{2} - 2\}$                          | 2-input gate          | <sup>"0"=0V, logic "1" = 16mV,<br/><math>C_1^p = C_2^p = \frac{1}{2}C = 0.5aF, C_L = 9aF, C_0 = 10aF,</math><br/><math>C_b = 9aF, C_j = 0.25aF, R_j = 10^5\Omega, V_b = 16mV</math></sup>                                                                                              |  |  |  |  |

| 2       | $Y_4 = X_2 \overline{X}_1 + X_2 X_0$<br>$Y_4 = sgn(X_0 + 2X_1 + 3X_2 - 4)$          | 3-input gate          | "0"=0V, logic "1" = 16mV, C=1aF, $C_1^{p} = \frac{1}{6}CC_2^{p} = \frac{1}{3}C$ ,<br>$C_2^{p} = \frac{1}{2}C = 0.5aF$ , $C_b = 9.75aF$ , $C_j = 0.25aF$ , $C_L = 9aF$ , Cj = 0.25aF, $C_0 = 10aF$ , $R_j = 10^5\Omega$ , $V_b = 16.19mV$ which is close to 16mV, so $V_b = V_s = 16mV$ |  |  |  |  |

|         | $P = (X_1 \cdot \overline{X}_2)$<br>$P = sgn \{ X_1 - X_2 - (1) \}$                 | 2-input gate          | "0"=0V, logic "1" = 16mV, $C_1^p = C_1^n = \frac{1}{2}C = 0.5aF$<br>, $C_L = 9aF$ , $C_0 = 9.5aF$ , $C_b = 9.5aF$ , $C_j = 0.25aF$ , $R_j = 10^5\Omega$ , $V_b = 16mV$                                                                                                                 |  |  |  |  |

| 3       | $Y=P + \overline{X}_1 \cdot X_2$<br>$Y = sgn\{-X_1+X_2+2P - (1)\}$                  | 3-input gate          | "0"=0V, logic "1" = 16mV, $C_1^n = C_1^p = \frac{1}{2}C_2^p = \frac{1}{4}C = 0.5aF, C_L = 9aF, C_0 = 9.5aF, C_b = 8.5aF, C_j = 0.25aF, R_j = 10^5\Omega$ , $V_b = 16mV$                                                                                                                |  |  |  |  |

|         | $Y_{3} = (X_{1} \bigoplus X_{2}) X_{0} = Y X_{0}$<br>$Y_{3} = sgn(Y + X_{0} - (2))$ | 2-input gate          | "0"=0V, logic "1" = 16mV, $C_1^p = C_2^p = \frac{1}{2}C = 0.5aF$<br>, $C_L = 9aF$ , $C_0 = 9.5aF$ , $C_b = 9.5aF$ , $C_j = 0.25aF$ , $R_j = 10^5\Omega$ , $V_b = 16mV$                                                                                                                 |  |  |  |  |

| 4       | $Y_{2} = X_{1} \overline{X}_{0}$<br>P = sgn { -X_{0}+X_{1}-(1) }                    | 2-input gate          | "0"=0V, logic "1" = 16mV, $C_1^n = C_1^p = \frac{1}{2}C = 0.5aF$<br>, $C_L = 9aF$ , $C_0 = 9.5aF$ , $C_b = 9.5aF$ , $C_j = 0.25aF$ , $R_j = 10^5\Omega$ , $V_b = 16mV$                                                                                                                 |  |  |  |  |

| 5       | $Y_1 = 0$                                                                           |                       |                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5       | $Y_0 = X_0$                                                                         |                       |                                                                                                                                                                                                                                                                                        |  |  |  |  |

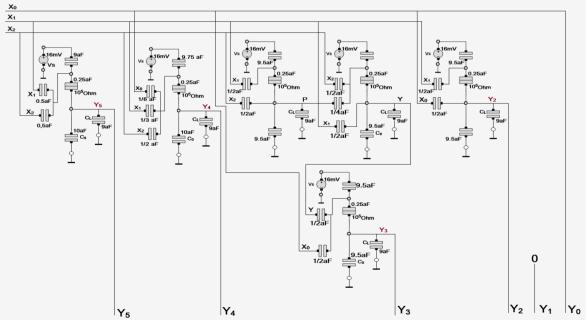

Now we will draw and set the threshold circuit for the simulation purpose. The simulation set is given in Fig.10.

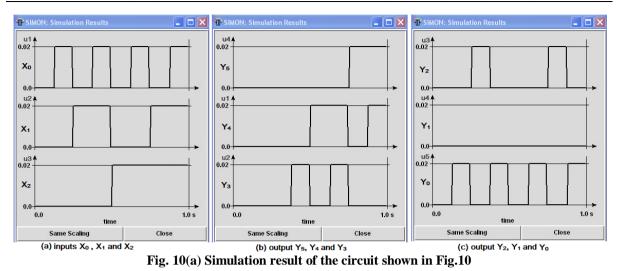

Fig. 10 Simulation set of creating square of 3-variable inputs of a ROM  $(8\times4)$  The simulation results of the Fig-10 using the simulator SIMON is provided in Fig. 10(a) below.

#### V. Discussion

In this work we have used 2-input and 3-input threshold logic gates and we have discussed regarding AND gate, Exclusive-OR gate and more complex combinational circuits to implement  $(2^3 \times 4)$  ROM as well as square circuit of the three input variables. The TLG circuits are drawn after analyzing their linear separable equations. Now we must discussed about their corresponding processing delays or speed. When we are going to find out processing delays, we will involve critical voltageV<sub>c</sub> along with the tunnel junction capacitanceC<sub>j</sub>. The switching or processing delay in connection with a logic gate/circuit can be checked by means of the approaches [8, 9] given as follows:

$Delay = -(e | ln (P_{error}) | R_t) / (|V_j| - V_c)^{\dots} (17)$

Here,  $V_i$  is the junction voltage and  $V_c$  is the critical voltage and  $R_t$  is the junction resistance.

The switching/tunneling event comes to happen as soon as the tunnel junction voltage  $V_j$  is greater than or equal to the critical voltage  $V_c$ , i.e.,  $|V_j| \ge V_c$ . When this conditional equation is satisfied by a 2-input AND gate then the resulting junction voltage of the AND gate gets the value  $V_j = 11.8$  mV, the internal critical voltage  $V_c$  of the tunnel junction becomes 11.58 mV. Given that tunnel resistance  $R_t = 10^5 \Omega$  and the probability of error change  $P_{error}$  is equal to  $10^{-12}$ . After measuring, the gate delay we get is  $0.062 |\ln(P_{error})|$  is = 2.21 ns. In this way we are able to find out the delays of gates and circuits listed in Table-5.

Whenever an electron passes through the tunnel junction, the total energy in the circuit gets changed. The distinct energy levels before and after the tunneling event are calculated with the equation (18).

$$\Delta E = E_{before\ tunnel} - E_{after\ tunnel} = -e(V_c - |V_j|)$$

(18)

This is the switching/tunneling energy  $-e(V_c - |V_j|)$  being consumed whenever a tunnel event happens in the tunneling circuit. The energy consumption for different circuits is given in Table-5 as well.

| Gate/Device          | elements    | Delay                                     | Switching<br>Energy |

|----------------------|-------------|-------------------------------------------|---------------------|

| inverter             | 9 elements  | $0.022 \ln(P_{error}) $ ns                | 10.40meV            |

| 2-input NOR          | 6 elements  | 0.060 ln( <i>P<sub>error</sub></i> )  ns  | 10.70meV            |

| 2-input OR           | 6 elements  | 0.050 ln( <i>P<sub>error</sub></i> )  ns  | 10.80meV            |

| 2-input NAND         | 6 elements  | 0.058 ln( <i>P<sub>error</sub></i> )  ns  | 10.70meV            |

| 2-input AND          | 6 elements  | 0.050 ln( <i>P<sub>error</sub></i> )  ns  | 10.80meV            |

| 3-input AND          | 7 elements  | 0.082 ln(P <sub>error</sub> )   ns        | 11.58 meV           |

| 3-input NAND         | 7 elements  | $0.072 \ln(P_{error}) $ ns                | 11.58 meV           |

| 2-input XOR          | 13 elements | 0.080 ln( <i>P<sub>error</sub></i> )  ns  | 21.20 meV           |

| 3-input OR           | 7 elements  | $0.082 \ln(P_{error}) $ ns                | 11.58 meV           |

| 3-input NOR          | 7 elements  | 0.082 ln( <i>P<sub>error</sub></i> )   ns | 11.55 meV           |

| Y5                   | 6 elements  | 0.050 ln( <i>P<sub>error</sub></i> )   ns | 10.80meV            |

| Y4                   | 6 elements  | $0.058 \ln(P_{error}) $ ns                | 10.80meV            |

| Y3                   | 19 elements | 0.158 ln( P <sub>error</sub> )  ns        | 32.25meV            |

| Y2                   | 6 elements  | 0.058 ln( <i>P<sub>error</sub></i> )  ns  | 10.80meV            |

| ROM $(2^3 \times 4)$ | 37 elements | 0.158 ln( <i>P<sub>error</sub></i> )  ns  | 32.25meV            |

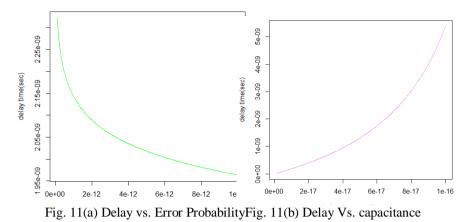

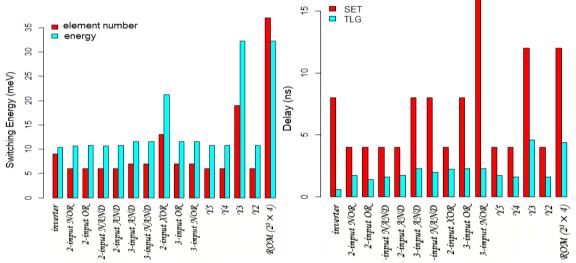

We have drawn curves relating to the switching delay vs. switching error probability in Fig. 11(a) and the switching delay vs. the unit capacitance C in Fig. 11(b).

We have measured / counted the total number of elements placed inany gate or circuit. We have provided the data collected from this work in connection withelement numbers, delays, and switching energy in Table-5.

Fig. 12 comparison of Elements and switching energyFig. 13 Bar diagram of delays of SET/TLG Vs. gates

The processing delays of distinct threshold logic circuits are different. For a 3-input OR gates, the processing delay is  $0.104|\ln(P_{error})|$  ns, for 2-input XOR gate it becomes  $0.102|\ln(P_{error})|$  ns, and inthe  $(2^3 \times 4)$  ROM circuit– delay forY<sub>5</sub> is  $0.062|\ln(P_{error})|$  ns, for Y<sub>4</sub>= $0.062|\ln(P_{error})|$  ns, for Y<sub>3</sub>= $0.186|\ln(P_{error})|$  ns, and for Y<sub>2</sub>= $0.062|\ln(P_{error})|$  ns.

Given the value of  $P_{error}=10^{-12}$ , so the time after which the first output of the Y<sub>3</sub>for the ROM circuit will fan out is 0.158|ln( $P_{error}$ )| ns =4.36 ns. This is the maximum delay time for ROM ( $2^3 \times 4$ ) also. So we are to maintain the input signal time i.e., after every 4.36 ns, we are to apply input signals. In this condition, the speed or frequency of the ROM ( $2^3 \times 4$ ) circuit will be 1/4.36 ns = 229.3MHz.

We are indeed interested in finding out the circuit delays anent CMOS, SET-based and LTG-based. The processing delay for a CMOS logic gate like AND, NAND, NOR, XOR is 12ns [15, 16], but the time required for tunneling through a single electron transistor (SET) [9, 10] is approximately 4ns [4, 5, 6, 7, 12, 13].

|              | Tuble 0            |                 |

|--------------|--------------------|-----------------|

| Gate/Device  | SET-based delay ns | LTG-based delay |

| inverter     | 8                  | 0.60 ns         |

| 2-input NOR  | 4                  | 1.71 ns         |

| 2-input OR   | 4                  | 1.38 ns         |

| 2-input NAND | 4                  | 1.60 ns         |

| 2-input AND  | 4                  | 1.71 ns         |

| 3-input AND  | 8                  | 2.26 ns         |

| Design of a Read-Onl | v Memory (ROM) | ) creating sa | uare of an i | iput using | Threshold |

|----------------------|----------------|---------------|--------------|------------|-----------|

|                      |                |               |              |            |           |

| 3-input NAND         | 8  | 1.98 ns |

|----------------------|----|---------|

| 2-input XOR          | 4  | 2.21 ns |

| 3-input OR           | 8  | 2.26 ns |

| 3-input NOR          | 16 | 2.26 ns |

| Y5                   | 4  | 1.71 ns |

| ¥4                   | 4  | 1.60 ns |

| ¥3                   | 12 | 4.36 ns |

| Y2                   | 4  | 1.60 ns |

| ROM $(2^3 \times 4)$ | 12 | 4.36 ns |

### Switching delays of SET and LTG

Assuming the error probability is  $10^{-12}$ , the delays for different gates/circuits we got are shown in Table-6. From the Table-6 we observe that the LTG based circuit is faster than the SET based circuit. The delays for SET and LTG gate based circuits are represented by a bar diagram in Fig13.

#### VI. Conclusion

ROM is an interesting device for us as the data will remain intact though power is OFF and then ON i.e. the ROM is not volatile. All the scientific data, constant numbers are stored in ROM. In the present work a square circuit for a 3 input variables, taking the help of a  $(2^3 \times 4)$ ROM, has been implemented. For implementing this ROM we have designed four functional units of four threshold logic expressions. After combining these four functional units and taking other two auxiliary output lines  $Y_1=0$  and  $Y_0=X_0$  we have drawn the full phases of the square circuit. For verification purpose, the input-output relationships are verified by using the SIMON simulator. The number of elements (single electron transistors, capacitances) used for different logic gates and other circuits, their processing delays, their power consumptions are listed in Tables. We have provided two related curves and two bar diagram for showing the relationships betweenDelay and Error Probability, Delay and capacitance, comparison of Elements and switching energy of different gates and lastly, Bar diagram of delays of SET/TLG vs. gates In this paper, we have visualized that the TLG based circuits are at least 2-times faster than SET based circuits. For the real operation, the temperature will be kept at 0K.

#### REFERENCES

- [1]. Anup Kumar Biswas, "Application of single electron threshold logic gates and memory elements to an up-down Counter" International Journal of Creative Research Thoughts (IJCRT) | Volume 9, Issue 6 June 2021 | ISSN: 2320-2882

- [2]. Anup Kumar Biswas, -"Implementation of A 4n-Bit Comparator based on IC Type 74L85 using Linear Threshold Gate Tunneling Technology" International Journal of Engineering Research & Technology ISSN: 2278-0181, Vol. 10 Issue 05, May-2021 pp.299-310.

- Anup Kumar Biswas, "State Transition Diagram for A Pipeline Unit based on Single Electron Tunneling" International Journal of [3]. Engineering Research & Technology (IJERT) Vol. 10 Issue 04, April-2021pp.325-336, ISSN: 2278-0181

- [4]. Anup Kumar Biswas, "Design of A Pipeline for A Fixed-Point Multiplication using Single Electron Tunneling Technology", International Journal of Engineering Research & Technology ISSN: 2278-0181, Vol. 10 Issue 04, April-2021 pp. 86-98,

- A. K. Biswas and S. K. Sarkar: "An arithmetic logic unit of a computer based on single electron transport system" [5]. (SPQEO)Semiconductor Physics, Quantum Electronics & Opt-Electronics. 2003. Vol 6. pp 91-96 No.1,

- A.K. Biswas and S. K. Sarkar: "Error Detection and Debugging on Information in Communication System Using Single Electron [6]. Circuit Based Binary Decision Diagram." (SPQEO) Semiconductor Physics Quantum electronics and opt electronics, Vol. 6, pp.1-8.2003

- Alexander N. Korotkov, "Single-electron logic and memory devices" INT. ELECTRONICS, 1999, Vol. 86, No. 5, 511-547 [7].

- Casper Lageweg, Student Member, IEEE, SorinCot ofan a, Senior Member, IEEE, and Stamatis Vassiliadis, Fellow, IEEE "Single [8]. Electron Encoded Latches and Flip-Flops" IEEE TRANS. ON NANOTECHNOLOGY, VOL. 3, NO. 2, JUNE 2004

- [9]. C. Lageweg, S. Cot, fan a, and S. Vassiliadis, "A linear threshold gate implementation in single electron technology," IEEE Computer Society VLSI Workshop, Apr. 2001, pp. 93

- [10]. K. Likharev, "Single-electron devices and their applications," Proc. IEEE, vol. 87, pp. 606-632, Apr. 1999.

- J. R. Tucker,- "Complementary digital logic based on the Coulomb-blockade", Journal of Applied Physics., vol. 72, no. 9, pp. [11]. 4399-4413, November 1992.

- Jacob. Millman and C. C. Halkias; "Integrated Electronics- Analog and Digital Circuits and Systems -second edition" McGraw Hill [12]. Education:

- [13]. Millman's Electronic Devices & Circuits 4th Edition (English, Paperback, Jacob Millman)

- [14]. M. Morris Mano, "Digital Logic and Computer Design" Second Edition PHI.

#### BIOGRAPHY

ANUP KUMAR BISWAS, born in 1971. He defended his Ph.D.[Engg.] thesis in 2005 in the stream of

Electronics and Telecommunication Endineering at Jadavpur University. He was a Senior Research Fellow(SRF) in Faculty of Engineering and Technology (FET) from 2002 to 2005 at the Department of Electronics &TC. Dr. Biswas has published 26 papers in national, international journals and conferences. The area of his scientific interests are computer arithmetic, parallel architectures, nanotechnology, and computer-aided design. He is engaged in research activities and teaching last 18 years.